第一章计算机系统知识(计算机组成原理)

计算机系统组成:运算器、控制器、存储器、输入设备与输出设备(外设)。

运算器、控制器等部件集成为中央处理器(cpu)。

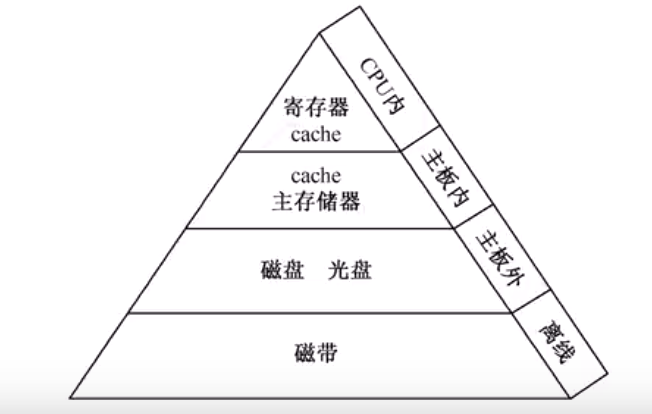

存储器由内部存储器和外部存储器。

cup+存储 = 主机(与现实主机区别)

计算机基础知识

中央处理器(cpu)

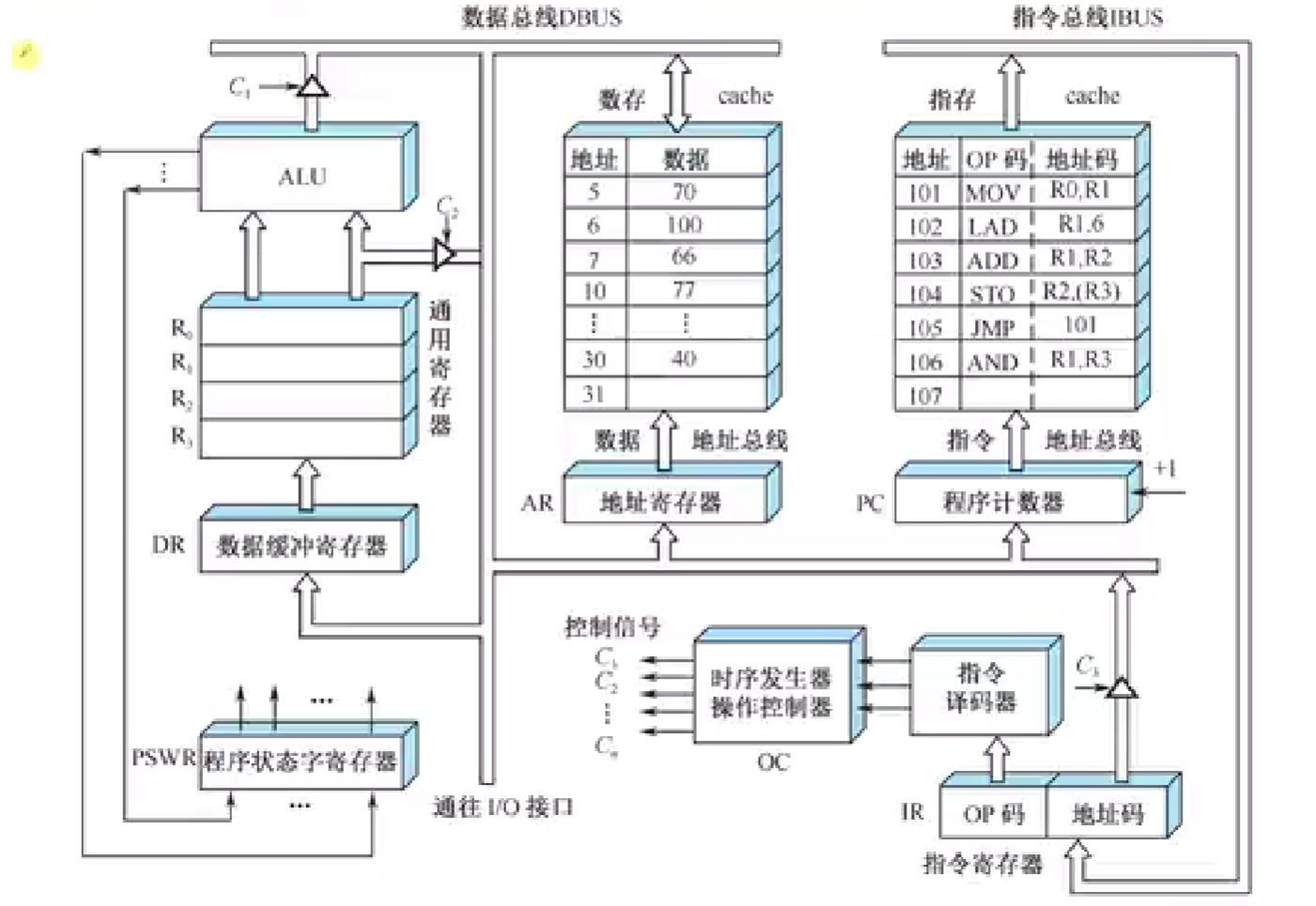

cpu主要由运算器、控制器、寄存器和内部总线等组成。

运算器和控制器的工作流程:

运算器

运算器是由算术逻辑单元(Arithmetic and Logic Unit,ALU)、累加寄存器(AC)、数据缓冲寄存器(DR)和状态条件寄存器(PSW)等组成,它是数据加工处理部件,用于完成计算机的各种算术和逻辑运算。

算术逻辑单元(ALU)。ALU是运算器的重要组成部件,负责处理数据,实现对数 据的算术运算和逻辑运算。

累加寄存器(AC)。AC通常简称为累加器,它是一个通用寄存器,其功能是当运算 器的算术逻辑单元执行算术或逻辑运算时,为ALU提供一个工作区。

数据缓冲寄存器(DR)。DR的主要作用为:作为CPU和内存、外部设备之间数据传送的中转站;作为CPU和内存、外围设备之间在操作速度上的缓冲;在单累加器结构的运算器中,数据缓冲寄存器还可兼作为操作数寄存器。

状态条件寄存器(PSW)。PSW保存由算术指令和逻辑指令运行或测试的结果建立的各种条件码内容,主要分为状态标志和控制标志,例如运算结果进位标志(C)、运算结果溢出标志(V)、运算结果为0标志(Z)等

控制器

指令 由操作码和地址码。

指令寄存器(IR)。IR存放指令操作。

程序计数器(PC)。PC具有寄存信息和计数两种功能,又称为指令计数器。会自增。

地址寄存器(AR)。AR保存当前CPU所访问的内存单元的地址。

**指令译码器(ID)**就是对指令中的操作码字段进行 分析解释,识别该指令规定的操作,向操作控制器发出具体的控制信号。

数据表示

2 8 16进制

位(b bit) -- 1B = 8b --> 字节(B byte) =

定点数:原码 反码 补码 移码。

反码 = 原码按位取反,负数时符号位(最高位)不变。

补码 = 与原码相同,负数时反码 + 1(可以将减法转换位加法) 移码 = 补码符号位取反

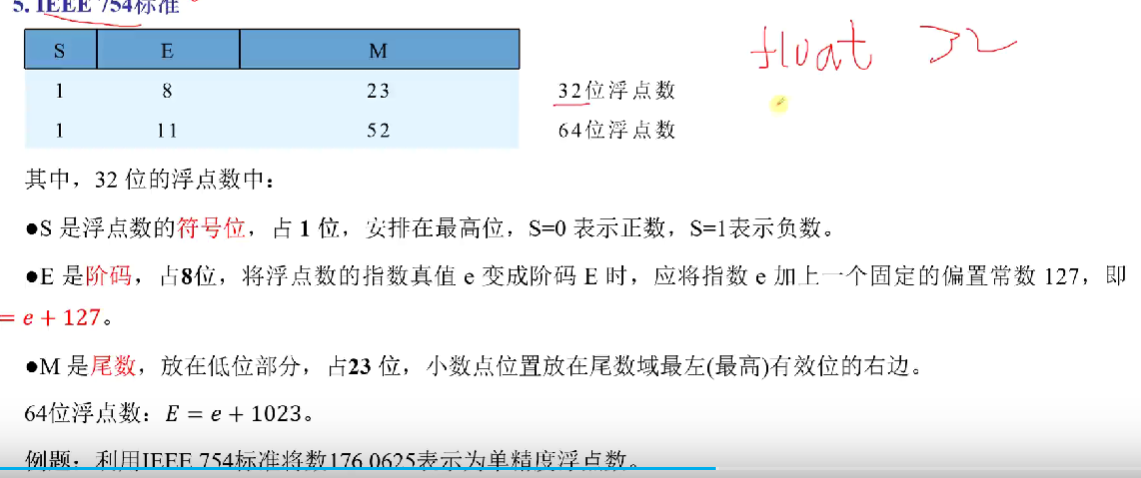

浮点数:使用IEEE 754标准 P8例题

对于32位浮点数:S符号位(1位) E(阶码 8位) M(尾数 23位)

校验码

奇偶校验码:增加了一个校验位,使得数据中的1的个数变成奇数或偶数。没有纠错功能

海明码:多重奇偶校验,n位数据满足一下k次校验码,如公式所示:

循环校验码

计算机体系结构

分类

指令系统

格式 :操作码(OP)和地址码(A)。

指令的寻址

顺序寻址:下一条指令由程序计数器PC给出的地址

跳跃寻址;吓一条指令由指令给出

操作数的寻址

大写字母的顺序表示速度的等级

立即寻址 ;即操作数本身,地址码==操作数。 A

直接寻址:操作数在内存的地址。 (C)

间接寻址: 操作数是要访问操作数的地址。(F)

寄存器寻址:操作数是寄存器的编号。还包含间接(D)和直接(B)

偏移寻址:相对(在pc上加入偏移) 基址(在地址上加入偏移) 变址(在变址上加入偏移)(E)

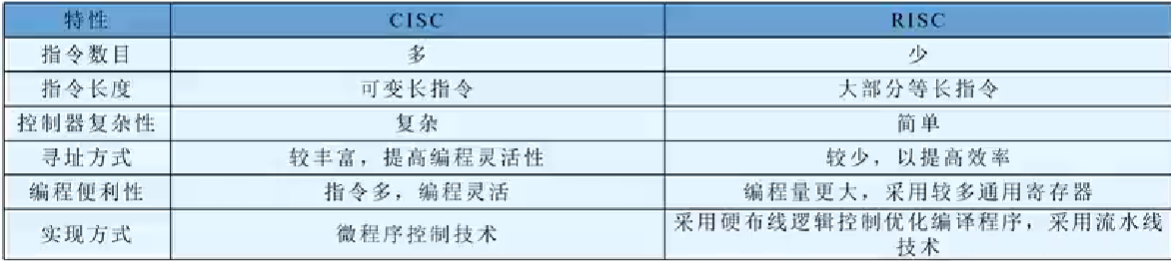

CISC 和 RISC

复杂指令集(CISC): 指令集庞大、指令是串行执行的。

精简指令集(RISC): 指令精简、采用优化编译、硬布线、重叠寄存器窗口等技术。

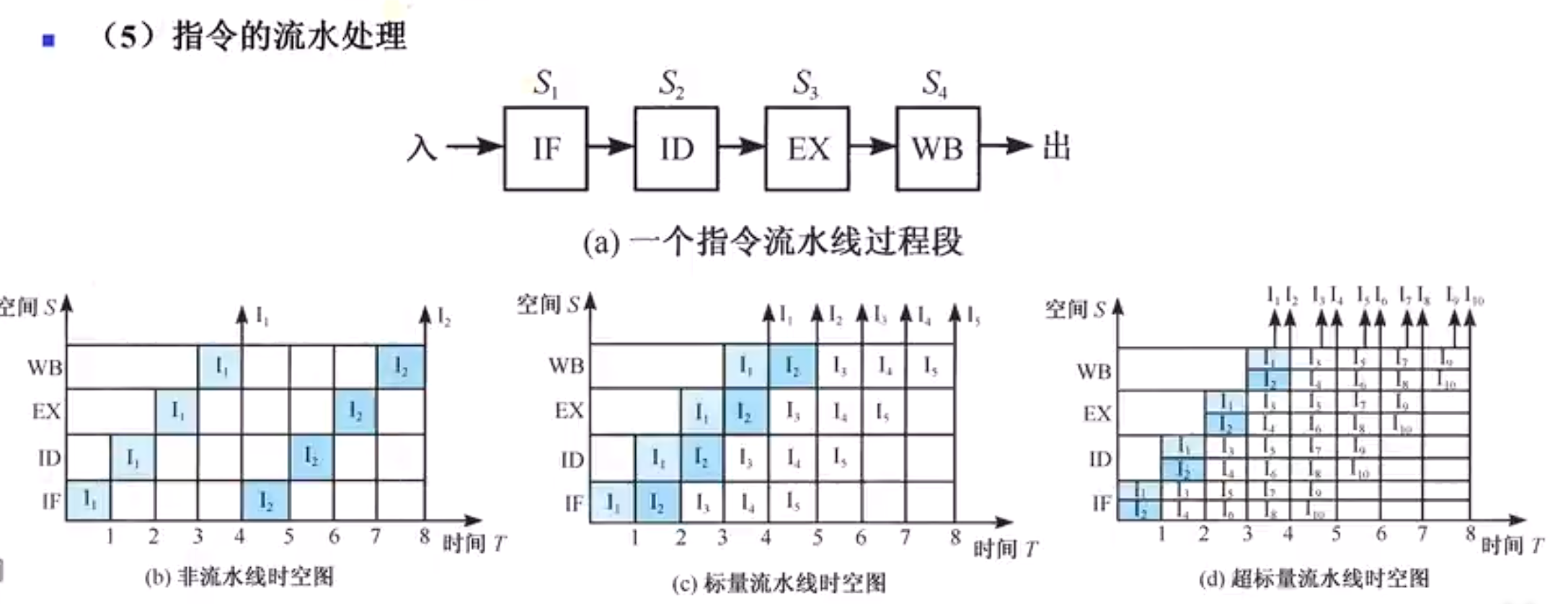

指令的流水处理

IF(取指令) ID(译码) EX(执行) WB(返回值) 图中是4个流水段

流水时间计算;n个流水段,每个流水段需要不同的时间。k条指令。

加速比:流水时间/非流水时间。

存储系统

cache--cpu L1

RAM

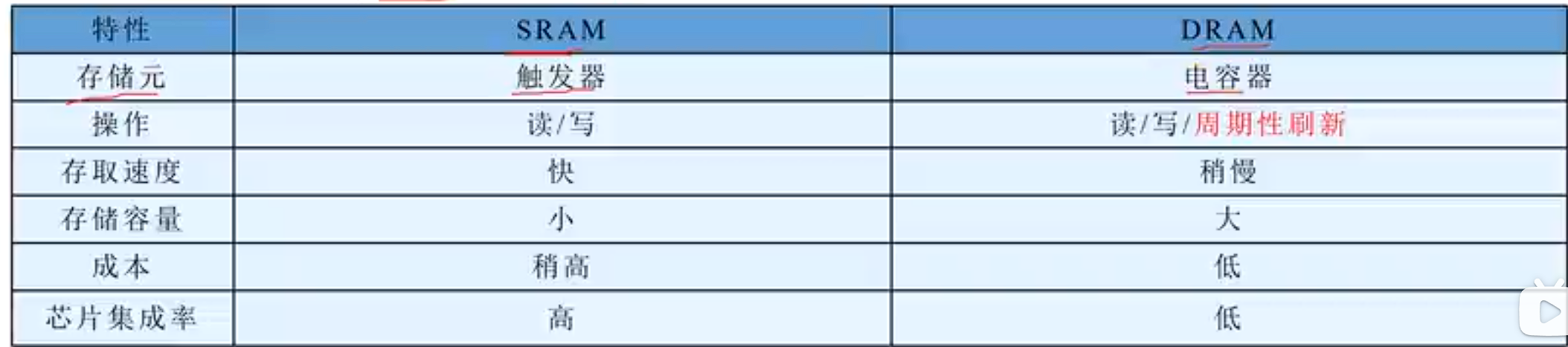

RAM(随机存储器);SRAM(静态)和DRAM(动态)。SRAM用于作为cache的存储,DRAM用于作为主存的存储,

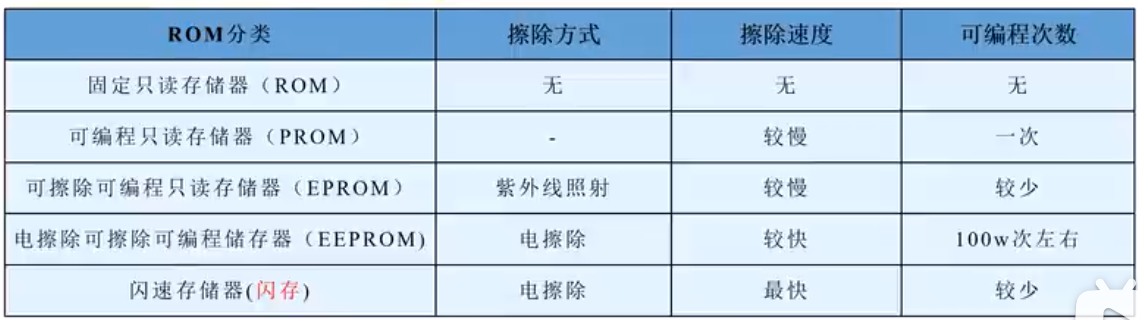

ROM

ROM(只读存储器);MAC地址存放的地方,有些只读存储器可以写但困难。

cache

高速缓存cache:在CPU与主存之间的存储器,介于主存与CPU之间的速度。解决了CPU与主存速度不匹配问题(效率问题)。理论依据是程序局部性原理。时间局部性(最近被访问过的指令可能再次访问)和空间局部性(最近访问的数据和指令往往存放在一片小的存储区域)。

主存与cache地址的映射: 全相连映射(将主存中的块可以放入cache中的任意一个空闲的行,利用率高,冲突少,但硬件不容易实现和慢,常用于小容量);直接映射(将主存中的块可以放入cache中对应的块号的取模,冲突多,硬件容易实现和快,常在大容量);组相连映射(将cache进行分组,主存中的块对组别数进行求模放入对应的组)。

虚拟存储器和磁盘

虚拟存储器:主存和辅存组成(外存)

磁盘:存取时间(寻道时间+旋转等待时间+数据传输时间)数据传输率(每秒能存取的字节数)

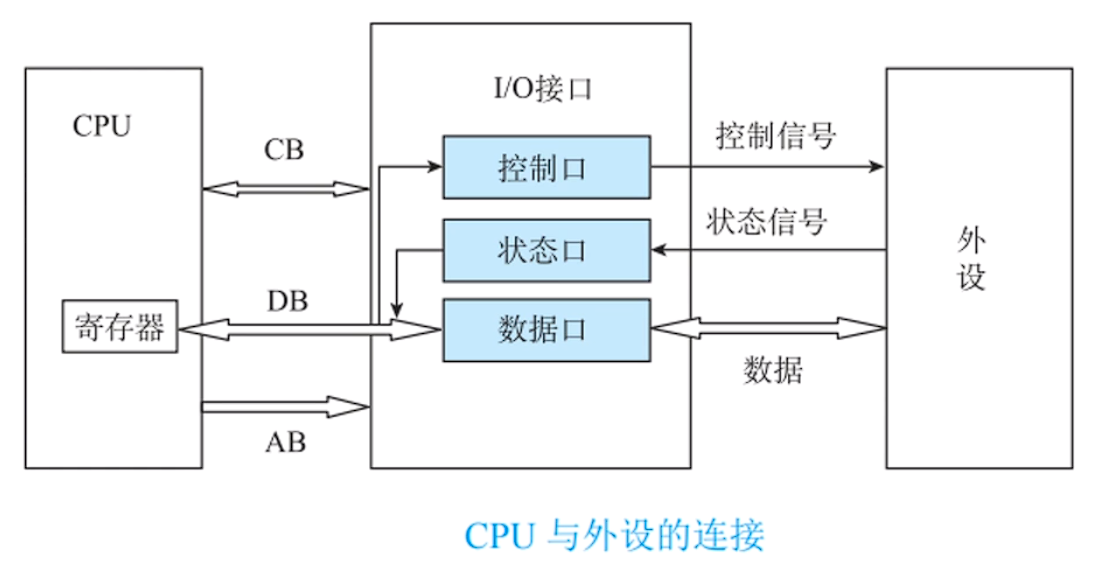

输入/输出

cpu通过I/O接口与外设进行数据交互。cpu与I/O接口的数据交互方式有:程序查询、程序中断、DMA、通道。

程序查询:CPU执行程序查询外设状态,不断判断,CPU与外设串行进行,占用cpu资源需要保护现场。适用低速、cpu不繁忙。

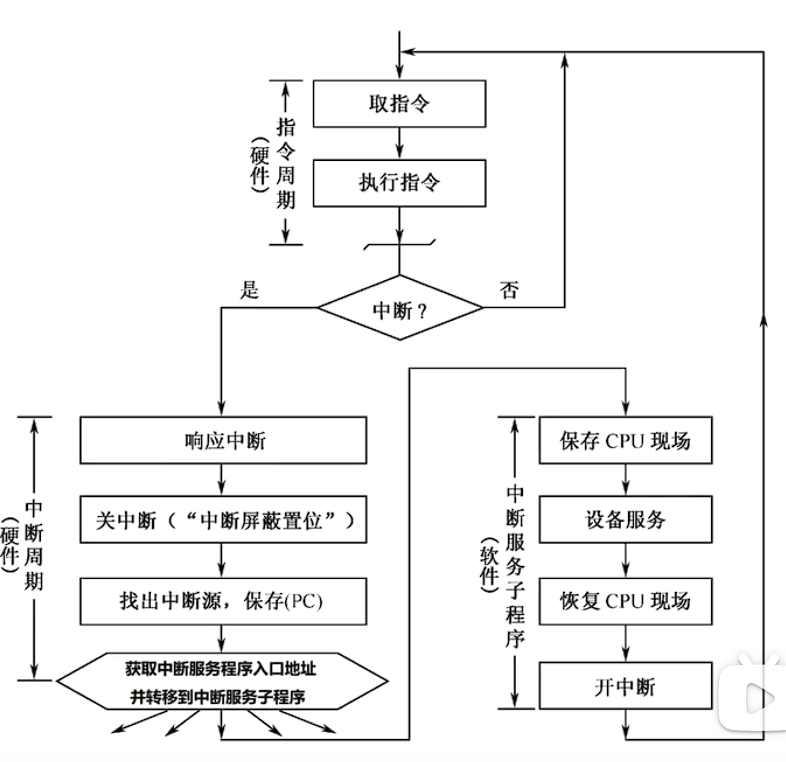

程序中断;在外设与I/O交换完数据后,发出中断信号让cpu处理中断,cpu 关中断--保护现场(为了正确返回之前执行的程序)-处理中断-恢复现场-开中断,中断程序的入口是中断向量。cpu和外设并行,硬件复杂,时间开销大,适用I/O实时性高的场景。

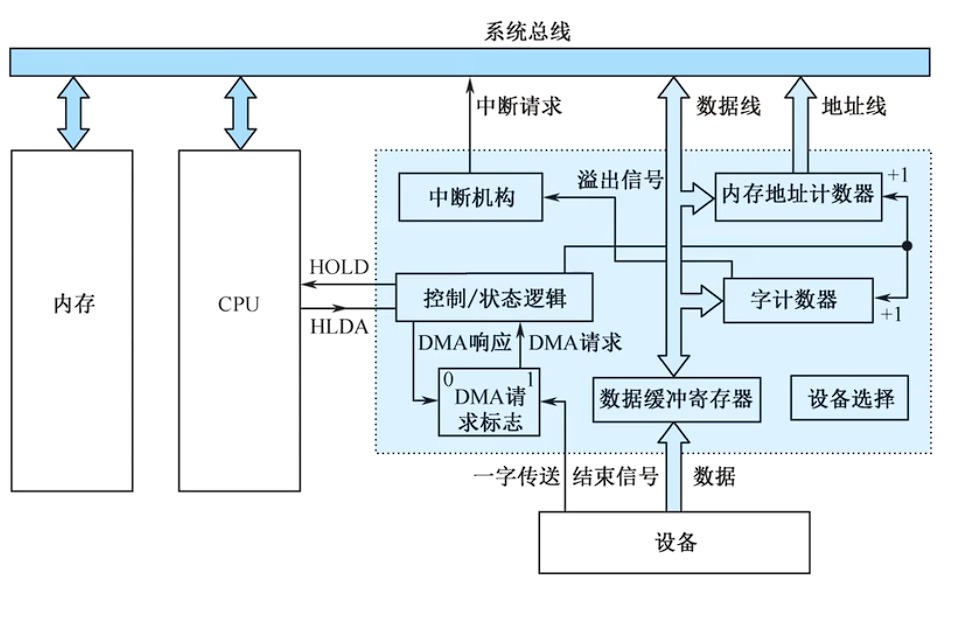

DMA:直接内存存取。DMA接管总线控制,在获取和释放权限时经过cpu,数据交换不经过cpu,可以直接访问内存。cpu与外设并行,读写是块,适合大批量的数据交换。

通道;通过输入输出处理机管理较多的外设。

总线系统

总线将计算机中的设备相互连接,它们传输数据的公共数据通道。

分类

(cpu内部)内部总线:cpu内部寄存器、运算器、控制器等的连接总线。

(cpu外部)系统总线;cpu与其他高速部件(主存、cache、I/O)之间的总线。数据总线(双向数据传输的总线,位数与存储字长、机器字长相关)、控制总线(传输各种控制和反馈信号)和地址总线(传输的数据目标的地址,单向传输,大小与主存大小相关取log2)。

I/O总线:I/O接口与外设的连接总线。

常见总线

PCI总线;微机上的内部总线,采用并行传输方式。

SCSI总线;小型计算机的外部总线,采用并行传输,在光盘、等

RS-232C(串行外部总线) USB(串行外部总线) IEEE-1349(串行外部总线) ** IEEE-488(并行外部总线)**

性能评价指标

信息安全的基本要素:机密 可审查 完整 可用 可控

加密与认证

对称加密

不公开加密算法。加密强度不高,只有一个密钥,不太安全。

常见:3DES、DES、AES、RC-5、IDEA

非对称加密

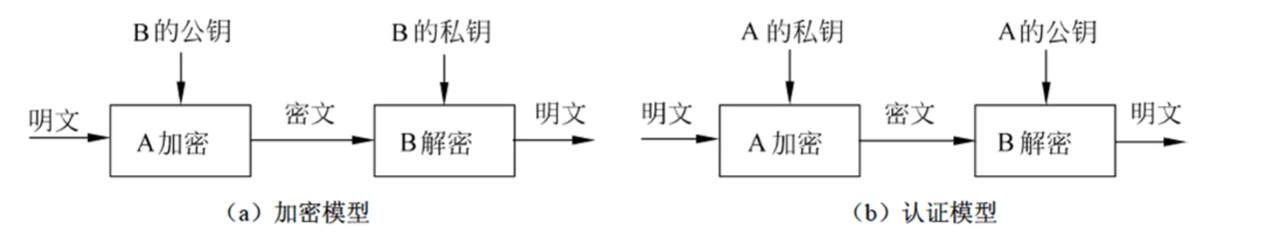

公钥和私钥(密钥),无需交换密钥。加密模型和认证模型。适用于少量数据,一般用于加密层加密。

常见:RSA

数字加密与签名

数字加密 (对密钥使用加密模型加密) 1、报文加密,通过对称加密,产生密钥。 2、发送方用接受方的公钥对上述密钥加密。 3、发送方将1和2的结果集合发送,称为数字信封。 4、接收方使用私钥解密得到密钥,在解密报文。

数字签名 (对信息摘要进行认证模型加密认证) 1、发送方通过单项散列算法(MD5)生成** 信息摘要**。 2、发送方通过自身私钥加密信息摘要。 3、发送方将1和2的结果集合发送 4、接收方通过信息使用同样的算法生成摘要,使用发送方的公钥进行信息验证和通过对比摘要,确认发送方的身份和信息是否篡改。

可靠性

可靠性就是正常运行的计算占比,可以视为概率。

串联系统;

并联系统: